HCPL-2611-020E Λογικός εξόδου Optoisolator 10MBd Schottky Clamped 5000Vrms 15kV/μs

| Τύπος | Περιγραφή |

| Κατηγορία | Συμπλέκτες (IC) |

| Ενσωματωμένο | |

| FPGA (Field Programmable Gate Array) | |

| Δρ. | Η εταιρεία Lattice Semiconductor |

| Σειρά | Επικαιροποίηση |

| Συσκευή | Τραπέζι |

| Αριθμός LAB/CLB | 3000 |

| Αριθμός λογικών στοιχείων/τμημάτων | 24000 |

| Συνολικά Μπιτ RAM | 1032192 |

| Αριθμός εισόδων/εξόδων | 197 |

| Πρόσθετη τάση | 10,04V ~ 1,155V |

| Τύπος στερέωσης | Επεξεργασία επιφανείας |

| Θερμοκρασία λειτουργίας | -40°C ~ 125°C (TJ) |

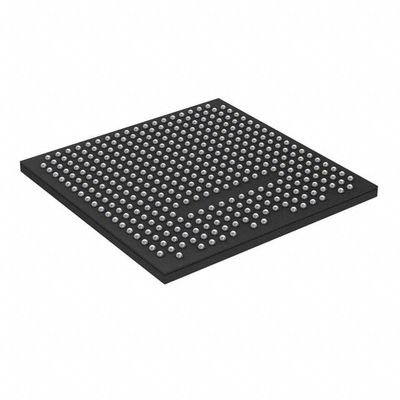

| Πακέτο / Κουτί | 381-FBGA |

| Πακέτο συσκευής του προμηθευτή | 381-CABGA (17x17) |

| Αριθμός βασικού προϊόντος | Επικαιροποίηση |

ΧαρακτηριστικάΕπικαιροποιημένο

* Μεγαλύτερη λογική πυκνότητα για αυξημένη ολοκλήρωση συστήματος

* 12K έως 44K LUT

* 197 έως 203 προγραμματιζόμενες από τον χρήστη I/O

* Ενσωματωμένα SERDES

* 270 Mb/s, έως 3,2 Gb/s, διεπαφή SERDES (ECP5UM Automotive)

* Υποστηρίζει eDP σε RDR (1,62 Gb/s) και HDR(2,7 Gb/s)

* Μέχρι τέσσερα κανάλια ανά συσκευή: PCI Express,Ethernet (1GbE, XAUI και SGMII) και CPRI

* sysDSPTM

* Πλήρως καταρρακτώδης αρχιτεκτονική τεμαχίων

* 12 έως 160 φέτες για υψηλή απόδοση πολλαπλασιασμού και συσσώρευσης

* Ενίσχυρες λειτουργίες ALU 54-bit

* Χρονοδιαίρεση Πολλαπλασιασμός Μοιράζοντας MAC

* Στρογγυλοποίηση και διακοπή

* Κάθε φέτα υποστηρίζει

* μισό 36 x 36, δύο 18 x 18 ή τέσσερις πολλαπλασιαστές 9 x 9

* Προχωρημένες 18 x 36 MAC και 18 x 18 πολλαπλασιασμός- πολλαπλασιασμός- συσσώρευση (MMAC)

* Ευέλικτοι πόροι μνήμης

* Μέχρι 1,944 Mb sysMEMTM Embedded Block RAM (EBR)

* 194K έως 351K bits κατανεμημένη μνήμη RAM

* sysCLOCK Αναλογικά PLL και DLL

* Τέσσερα DLL και τέσσερα PLL στο LAE5-45; δύο DLL και δύο PLL στο LAE5-25 και στο LAE5-12

* Προετοιμασμένη Σύγχρονη Εισαγωγή/Εξαγωγή Πηγής

* Μητρώα DDR σε κυψέλες I/O

* Ειδική λειτουργία ισοπέδωσης ανάγνωσης/γράφησης

* Ειδική λογική ταχυτήτων

* Υποστήριξη των συγχρονισμένων προτύπων

* ADC/ DAC, 7:1 LVDS, XGMII

* Συσκευές υψηλής ταχύτητας ADC/ DAC

* Ειδική υποστήριξη μνήμης DDR2/DDR3 και LPDDR2/LPDDR3 με λογική DQS, ταχύτητα δεδομένων έως 800 Mb/s

* Προγραμματιζόμενο sysI/OTM Buffer υποστηρίζει ευρύτατα

Διάλογος διεπαφών

* Τερματισμός στο τσιπ

* LVTTL και LVCMOS 33/ 25/18/15/12

* SSTL 18/15 Ι, ΙΙ

* HSUL12

* LVDS, Bus-LVDS, LVPECL, RSDS, MLVDS

* υποLVDS και SLVS, MIPI D-PHY διεπαφές εισόδου

* Ευέλικτη διαμόρφωση συσκευής

* Κοινή τράπεζα για τη διαμόρφωση I/O

* Διασύνδεση flash εκκίνησης SPI

* Υποστηρίζεται η υποστήριξη εικόνων διπλής εκκίνησης

* Σκλάβος SPI

* TransFRTM I/ O για απλές ενημερώσεις πεδίου

* Στήριξη για την άμβλυνση της διαταραχής ενός ενιαίου γεγονότος (SEU)

* Ανίχνευση ελαφρού σφάλματος

* Διόρθωση ήπιων σφαλμάτων Χωρίς διακοπή της λειτουργίας του χρήστη

* Ενέχυση μαλακών σφαλμάτων Emulate SEU event to debug system error handling

* Υποστήριξη σε επίπεδο συστήματος

* Συμμόρφωση με τα πρότυπα IEEE 1149.1 και IEEE 1532

* Ανακαλύψτε λογικό αναλυτή

* Οσιλατήρας σε τσιπ για εκκίνηση και γενική χρήση

* 1.1 V πυρήνας τροφοδοσίας

ΠεριγραφέςΕπικαιροποιημένο

Η οικογένεια συσκευών FPGA ECP5 Automotive είναι βελτιστοποιημένη για να παρέχει υψηλές επιδόσεις, όπως:

μια βελτιωμένη αρχιτεκτονική DSP, υψηλής ταχύτητας SERDES και υψηλής ταχύτητας συγχρονισμένες διεπαφές πηγής σε ένα

οικονομικό ύφασμα FPGA.

Περιβαλλοντικές και εξαγωγικές ταξινόμησηΕπικαιροποιημένο

| ΑΤΡΙΒΟΥΤ | Περιγραφή |

| Κατάσταση RoHS | Συμμόρφωση με την οδηγία ROHS3 |

| Επίπεδο ευαισθησίας στην υγρασία (MSL) | 3 (168 ώρες) |

| Το καθεστώς REACH | REACH Μη επηρεασμένη |

| Εθνική Εθνική Εταιρεία | EAR99 |

| HTSUS | 8542.39.0001 |

![]()